Come Sintetizzare e Programmare una GAL nel 2023 con il VHDL

Ha ancora senso parlare di GAL (Generic Array Logic) nel 2023? Probabilmente no per i nuovi progetti ma potrebbe averlo quando si parla di riparazioni di vecchie schede elettroniche. Tra la metà degli anni ‘80 e la metà degli anni ’90 le PLA (Programmable Logic Array) e le GAL venivano impiegate in moltissimi design elettronici, non è quindi difficile imbattersi in questi dispositivi su schede in riparazione. Ovviamente, non potevo non imbattermi in una scheda elettronica proprio con una GAL guasta e da ripristinare o meglio da sostituire completamente con una nuova GAL. Di questa scheda prodotta da SEGA (si, proprio la SEGA produttrice di videogiochi) ne parleremo in vari altri articoli successivi andando a vedere proprio come fare un reverse engineering della scheda per ricreare il codice logico della GAL. Per i più curiosi aggiungo che si tratta della Driver Feedback Board di un cabinato SEGA Rally 2 costituita da uno Z80, EEPROM con istruzioni macchina, SRAM per la memoria dati e da altre bellezze. Insomma, una scheda veramente eccezionale progettata da quei miti, anch’essi eccezionali, del team AM4 della SEGA.

In questo articolo andremo a vedere come sintetizzare il codice per una GAL16V8 e come programmarla con strumenti attuali.

Premetto che l’articolo è incentrato sulla GAL16V8 che veniva prodotta da Lattice (adesso l’equivalente è ancor prodotta dalla Atmel con nome ATF16V8) ma le nozioni sono valide per qualsiasi modello di GAL come, ad esempio, la popolarissima GAL22V10. Inoltre, la scrittura dell’articolo da per scontato che sia già nota cosa sia una GAL e sia nota, almeno a grandi linee, la sua architettura interna. Wikipedia ed i vari datasheet dei componenti in questo possono essere di grande aiuto.

GAL16V8D

Fatta questa doverosa premessa possiamo dividere in due parti la programmazione di una GAL:

- Scrittura del codice sorgente e generazione del file di programmazione JEDEC;

- Programmazione della GAL con il file JEDEC tramite programmatore dedicato.

Scrittura del codice sorgente e generazione JEDEC

Negli anni di massimo utilizzo delle GAL vi erano molti software di sintesi sia per Windows che per MS-DOS e le GAL venivano descritte con linguaggi come il PALASM, l’ABEL o il CUPL. Oggi giorno questi linguaggi sono, seppur sempre validi, sicuramente stati superati da linguaggi più moderni come il Verilog ed il VHDL comunemente utilizzati per la descrizione dell’hardware nelle FPGA (considerabili come l’evoluzione delle GAL) e negli ASIC. Il mio scopo era, quindi, riuscire a sfruttare un linguaggio moderno, in particolare il VHDL, per scrivere le equazioni booleane da implementare nella GAL. Per fare questo lo scoglio era riuscire a trovare un software capace di interpretare il VHDL e capace di sintetizzarlo per la GAL16V8.

Per fortuna tutt’oggi tale software esiste ed è prodotto dalla “mamma” delle GAL ovvero da Lattice Semiconductors.

Tale software si chiama ispLEVER Classic (alla versione 2.1 ad agosto 2023) ed è liberamente scaricabile dal sito della Lattice al seguente link: https://www.latticesemi.com/ispleverclassic

Per la programmazione delle GAL è sufficiente soltanto il pacchetto base (ispLEVER Classic 2.1 Base Module) e nessun’altro pacchetto scaricabile.

Download ISPLever Classic

Inoltre, chiarisco subito che il software gira soltanto su Windows XP o Windows 7 quindi se avete Windows 10 o superiore l’unica possibilità che avete (come ho fatto io) è di crearvi una macchina virtuale con Windows XP (o 7). Sul sito della Lattice è presente una patch per Windows 10 ma non produce i risultati desiderati nel senso che alcuni software basilari su Windows 10 si rifiutano di funzionare bloccandosi in alcuni punti mentre su Windows XP tutto funziona perfettamente (la patch in realtà è per i driver non per il software come potrebbe sembrare). Un’ultima nota: per motivi storici ed a mio avviso oramai nel 2023 senza più senso, ispLEVER Classic è un software a pagamento che richiede quindi una licenza. Contattando la Lattice o il proprio rivenditore si possono avere licenze temporanee di prova.

Installato il software mettetelo da parte in quanto ci servirà soltanto alla fine della procedura per generare il file JEDEC. La prima cosa da fare è, quindi, descrivere la logica che vogliamo far implementare alla GAL in VHDL. Non mi dilungherò sul VHDL o su come scrivere un Entity in quanto non è lo scopo di questo articolo. A titolo esemplificativo, consideriamo, ad esempio, questo file VHDL che descrive alcune semplici equazioni booleane che vogliamo sintetizzare.

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 |

---------------------------------------------------------------- -- -- Project: GAL16V8 Test -- Company: ACEInnova -- -- Module name: e_SR2DriverBoard -- Description: Test File for GAL16V8 -- -- File Name: e_SR2DriverBoard.vhd -- -- Author: Alessio Carpini -- Revision: 1.1 -- Date: 04-08-2023 -- ---------------------------------------------------------------- LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.NUMERIC_STD.ALL; ENTITY e_SR2DriverBoard IS PORT ( -- Input PIN l_SR2DriverBoardInPin1_i : IN STD_LOGIC; l_SR2DriverBoardInPin2_i : IN STD_LOGIC; l_SR2DriverBoardInPin3_i : IN STD_LOGIC; l_SR2DriverBoardInPin4_i : IN STD_LOGIC; l_SR2DriverBoardInPin5_i : IN STD_LOGIC; l_SR2DriverBoardInPin6_i : IN STD_LOGIC; l_SR2DriverBoardInPin7_i : IN STD_LOGIC; l_SR2DriverBoardInPin8_i : IN STD_LOGIC; l_SR2DriverBoardInPin9_i : IN STD_LOGIC; l_SR2DriverBoardInPin11_i : IN STD_LOGIC; -- Output PIN l_SR2DriverBoardInPin12_o : OUT STD_LOGIC; l_SR2DriverBoardInPin13_o : OUT STD_LOGIC; l_SR2DriverBoardInPin14_o : OUT STD_LOGIC; l_SR2DriverBoardInPin15_o : OUT STD_LOGIC; l_SR2DriverBoardInPin16_o : OUT STD_LOGIC; l_SR2DriverBoardInPin17_o : OUT STD_LOGIC; l_SR2DriverBoardInPin18_o : OUT STD_LOGIC; l_SR2DriverBoardInPin19_o : OUT STD_LOGIC ); END e_SR2DriverBoard; ARCHITECTURE a_SR2DriverBoard OF e_SR2DriverBoard IS SIGNAL l_toggleOutput_s : STD_LOGIC; SIGNAL l_outputEnable_s : STD_LOGIC; BEGIN l_toggleOutput_s <= l_SR2DriverBoardInPin8_i AND l_SR2DriverBoardInPin9_i AND l_SR2DriverBoardInPin11_i; l_outputEnable_s <= NOT(l_SR2DriverBoardInPin5_i) OR l_SR2DriverBoardInPin6_i OR l_SR2DriverBoardInPin7_i; l_SR2DriverBoardInPin12_o <= l_toggleOutput_s; l_SR2DriverBoardInPin13_o <= NOT(l_toggleOutput_s); l_SR2DriverBoardInPin14_o <= l_outputEnable_s OR l_SR2DriverBoardInPin3_i OR l_SR2DriverBoardInPin2_i; l_SR2DriverBoardInPin15_o <= l_outputEnable_s OR NOT(l_SR2DriverBoardInPin2_i); l_SR2DriverBoardInPin16_o <= l_outputEnable_s OR l_SR2DriverBoardInPin3_i; l_SR2DriverBoardInPin17_o <= l_outputEnable_s AND l_SR2DriverBoardInPin3_i; l_SR2DriverBoardInPin18_o <= l_outputEnable_s OR l_SR2DriverBoardInPin3_i OR NOT(l_SR2DriverBoardInPin2_i); l_SR2DriverBoardInPin19_o <= NOT(l_SR2DriverBoardInPin5_i XOR l_SR2DriverBoardInPin6_i XOR l_SR2DriverBoardInPin7_i); END ARCHITECTURE a_SR2DriverBoard; |

Il file VHDL è molto semplice. Contiene una serie di INPUT, che rappresentano gli input della GAL16V8 ed una serie di segnali di OUTPUT che rappresentano gli output della nostra GAL16V8. Infine, nel VHDL sono descritte le relazioni logiche tra gli ingressi (gli INPUT) e le uscite (gli OUTPUT). Notare che sono tutte logiche combinatorie relativamente semplici proprio perché ad una GAL non si può chiedere molto di più.

A questo punto che il VHDL è stato realizzato, è necessario assegnare i vari segnali di INPUT ed OUTPUT, scritti nel file VHDL, ai pin fisici della GAL. Questa operazione di assegnazione viene fatta tramite l’attributo “LOC” che viene interpretato da ISPLever Classic per effettuare le assegnazioni durante la sintesi del codice. L’attributo ha la seguente sintassi:

|

1 |

attribute LOC of [SigName] : signal is "[pin#]"; |

Quindi, completiamo il file VHDL, precedentemente scritto, in questo modo:

|

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 87 88 89 90 91 |

---------------------------------------------------------------- -- -- Project: GAL16V8 Test -- Company: ACEInnova -- -- Module name: e_SR2DriverBoard -- Description: Test File for GAL16V8 -- -- File Name: e_SR2DriverBoard.vhd -- -- Author: Alessio Carpini -- Revision: 1.1 -- Date: 04-08-2023 -- ---------------------------------------------------------------- LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.NUMERIC_STD.ALL; ENTITY e_SR2DriverBoard IS PORT ( -- Input PIN l_SR2DriverBoardInPin1_i : IN STD_LOGIC; l_SR2DriverBoardInPin2_i : IN STD_LOGIC; l_SR2DriverBoardInPin3_i : IN STD_LOGIC; l_SR2DriverBoardInPin4_i : IN STD_LOGIC; l_SR2DriverBoardInPin5_i : IN STD_LOGIC; l_SR2DriverBoardInPin6_i : IN STD_LOGIC; l_SR2DriverBoardInPin7_i : IN STD_LOGIC; l_SR2DriverBoardInPin8_i : IN STD_LOGIC; l_SR2DriverBoardInPin9_i : IN STD_LOGIC; l_SR2DriverBoardInPin11_i : IN STD_LOGIC; -- Output PIN l_SR2DriverBoardInPin12_o : OUT STD_LOGIC; l_SR2DriverBoardInPin13_o : OUT STD_LOGIC; l_SR2DriverBoardInPin14_o : OUT STD_LOGIC; l_SR2DriverBoardInPin15_o : OUT STD_LOGIC; l_SR2DriverBoardInPin16_o : OUT STD_LOGIC; l_SR2DriverBoardInPin17_o : OUT STD_LOGIC; l_SR2DriverBoardInPin18_o : OUT STD_LOGIC; l_SR2DriverBoardInPin19_o : OUT STD_LOGIC ); --The syntax of attribute LOC --attribute LOC : string; --attribute LOC of [SigName] : signal is "[pin#]"; attribute LOC : string; attribute LOC of l_SR2DriverBoardInPin1_i : signal is "1"; attribute LOC of l_SR2DriverBoardInPin2_i : signal is "2"; attribute LOC of l_SR2DriverBoardInPin3_i : signal is "3"; attribute LOC of l_SR2DriverBoardInPin4_i : signal is "4"; attribute LOC of l_SR2DriverBoardInPin5_i : signal is "5"; attribute LOC of l_SR2DriverBoardInPin6_i : signal is "6"; attribute LOC of l_SR2DriverBoardInPin7_i : signal is "7"; attribute LOC of l_SR2DriverBoardInPin8_i : signal is "8"; attribute LOC of l_SR2DriverBoardInPin9_i : signal is "9"; attribute LOC of l_SR2DriverBoardInPin11_i : signal is "11"; attribute LOC of l_SR2DriverBoardInPin12_o : signal is "12"; attribute LOC of l_SR2DriverBoardInPin13_o : signal is "13"; attribute LOC of l_SR2DriverBoardInPin14_o : signal is "14"; attribute LOC of l_SR2DriverBoardInPin15_o : signal is "15"; attribute LOC of l_SR2DriverBoardInPin16_o : signal is "16"; attribute LOC of l_SR2DriverBoardInPin17_o : signal is "17"; attribute LOC of l_SR2DriverBoardInPin18_o : signal is "18"; attribute LOC of l_SR2DriverBoardInPin19_o : signal is "19"; END e_SR2DriverBoard; ARCHITECTURE a_SR2DriverBoard OF e_SR2DriverBoard IS SIGNAL l_toggleOutput_s : STD_LOGIC; SIGNAL l_outputEnable_s : STD_LOGIC; BEGIN l_toggleOutput_s <= l_SR2DriverBoardInPin8_i AND l_SR2DriverBoardInPin9_i AND l_SR2DriverBoardInPin11_i; l_outputEnable_s <= NOT(l_SR2DriverBoardInPin5_i) OR l_SR2DriverBoardInPin6_i OR l_SR2DriverBoardInPin7_i; l_SR2DriverBoardInPin12_o <= l_toggleOutput_s; l_SR2DriverBoardInPin13_o <= NOT(l_toggleOutput_s); l_SR2DriverBoardInPin14_o <= l_outputEnable_s OR l_SR2DriverBoardInPin3_i OR l_SR2DriverBoardInPin2_i; l_SR2DriverBoardInPin15_o <= l_outputEnable_s OR NOT(l_SR2DriverBoardInPin2_i); l_SR2DriverBoardInPin16_o <= l_outputEnable_s OR l_SR2DriverBoardInPin3_i; l_SR2DriverBoardInPin17_o <= l_outputEnable_s AND l_SR2DriverBoardInPin3_i; l_SR2DriverBoardInPin18_o <= l_outputEnable_s OR l_SR2DriverBoardInPin3_i OR NOT(l_SR2DriverBoardInPin2_i); l_SR2DriverBoardInPin19_o <= NOT(l_SR2DriverBoardInPin5_i XOR l_SR2DriverBoardInPin6_i XOR l_SR2DriverBoardInPin7_i); END ARCHITECTURE a_SR2DriverBoard; |

A questo punto il file VHDL contiene sia la logica che le assegnazioni dei pin e può essere quindi dato in pasto ad ispLEVER Classic. Anche in questo caso la cosa è piuttosto facile. Tra tutti i software che compongono la suite di ispLEVER, quello principale è “ispLEVER Classic Project Navigator”.

ispLEVER Classic Project Navigator

Apriamo tale software e creiamo un nuovo progetto in VHDL e per la GAL specifica. Per farlo spostarsi in “File -> New Project”, scegliere il nome del progetto e definire che si tratta di un progetto in VHDL e che deve essere utilizzato Synplify come tool di sintesi (tool integrato in ispLEVER Classic).

ispLEVER Project

Premere “Avanti” e selezionare il dispositivo desiderato. Nel caso dell’esempio proposto, dovrà essere spuntato “Show Obsolete Devices” per fare apparire la lista delle GAL supportate e poi scegliere il modello di GAL desiderato.

ispLEVER Project GAL

Infine, nella successiva schermata dovrà essere scelto il file VHDL precedentemente realizzato e selezionare che si tratta di un VHDL Module e non di un Testbench, ovviamente.

ispLEVER Project VHDL

A questo punto la situazione dovrebbe essere quella di figura.

ispLEVER Project Window

Cliccare sul file VHDL con il tasto destro e scegliere “Set as Active Top Module” per impostarlo come file di TOP.

ispLEVER Top Module

Successivamente selezionare “GAL16V8D-15LP” e premere due volte a destra su “JEDEC file” per avviare la sintesi e la generazione del file di programmazione oppure, in modo del tutto equivalente, cliccare su “Process -> Start”.

Se tutto è andato a buon fine, il software avrà prodotto un file JEDEC (.jed), che dovrà essere utilizzato in fase di programmazione, e saranno apparse le spunte verdi nei vari step del processo come da figura seguente. Il software permette anche impostazioni particolari dei FUSES che vanno oltre l’obiettivo di questo articolo. Se interessati potete leggere la guida integrata in ispLEVER Classic ove sono spiegate tali impostazioni.

ispLEVER JEDEC

Il file JEDEC creato si trova nella root della cartella del progetto:

ispLEVER JEDEC file

Programmazione della GAL con file JEDEC

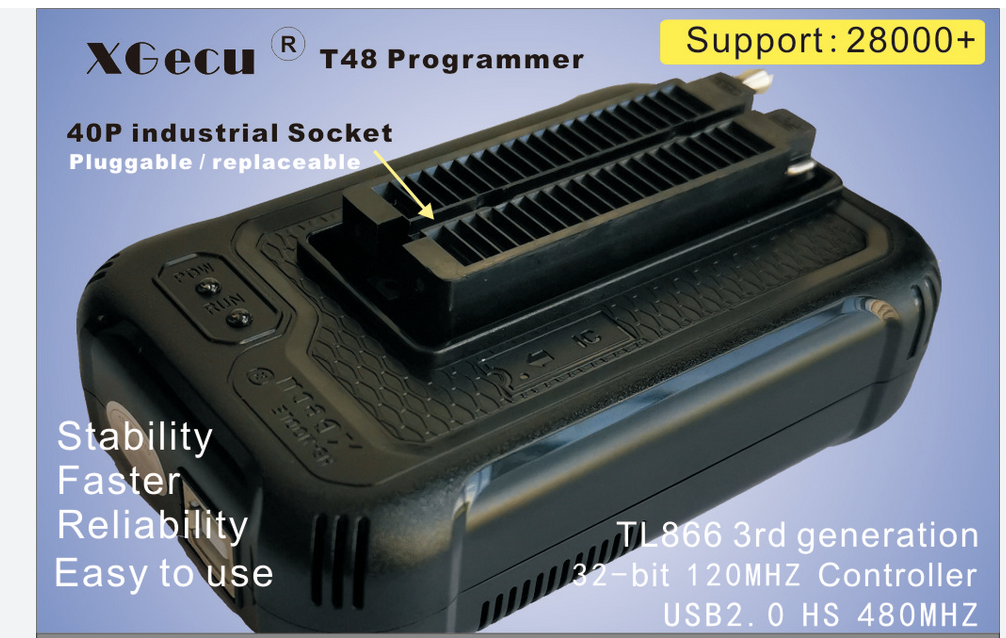

La programmazione delle GAL può essere fatta in diversi modi, sia costruendosi in proprio un programmatore (fare una ricerca su Google e su GitHub) sia cercando su ebay o in qualche mercatino un vecchio programmatore con porta parallela o seriale. Io però desideravo un programmatore moderno funzionante su USB e sugli ultimi sistemi operativi Windows. In aiuto ci viene il programmatore universale T48 (XGecu T48 Universal Programmer) della XGecu che non solo è in grado di programmare e leggere le GAL ma una moltitudine di altri integrati programmabili (vedere la lista qui). Il programmatore può essere acquistato a circa 60€ oppure a cifre più alte se oltre al programmatore si desiderano anche le schede di adattamento.

XGecu T48 Programmer

Ho testato il T48 sia per le GAL che per altro IC e non mi ha mai dato problemi, quindi non posso che esserne soddisfatto. Unica nota molto importante: il programmatore vuole une tensione via USB molto stabile e non troppo distante dai 5V. Se il PC non fosse in grado di fornirla direttamente, il software di programmazione all’apertura fornirebbe un errore. Unico modo per risolvere facilmente la cosa, utilizzare un hub USB alimentato esternamente.

La programmazione utilizzando il programmatore T48 si effettua aprendo il software di programmazione Xgpro (totalmente gratuito e scaricabile direttamente dal sito del produttore) arrivato alla versione 12.60 nel momento in cui scrivo.

T48 Programmer Xgpro Software

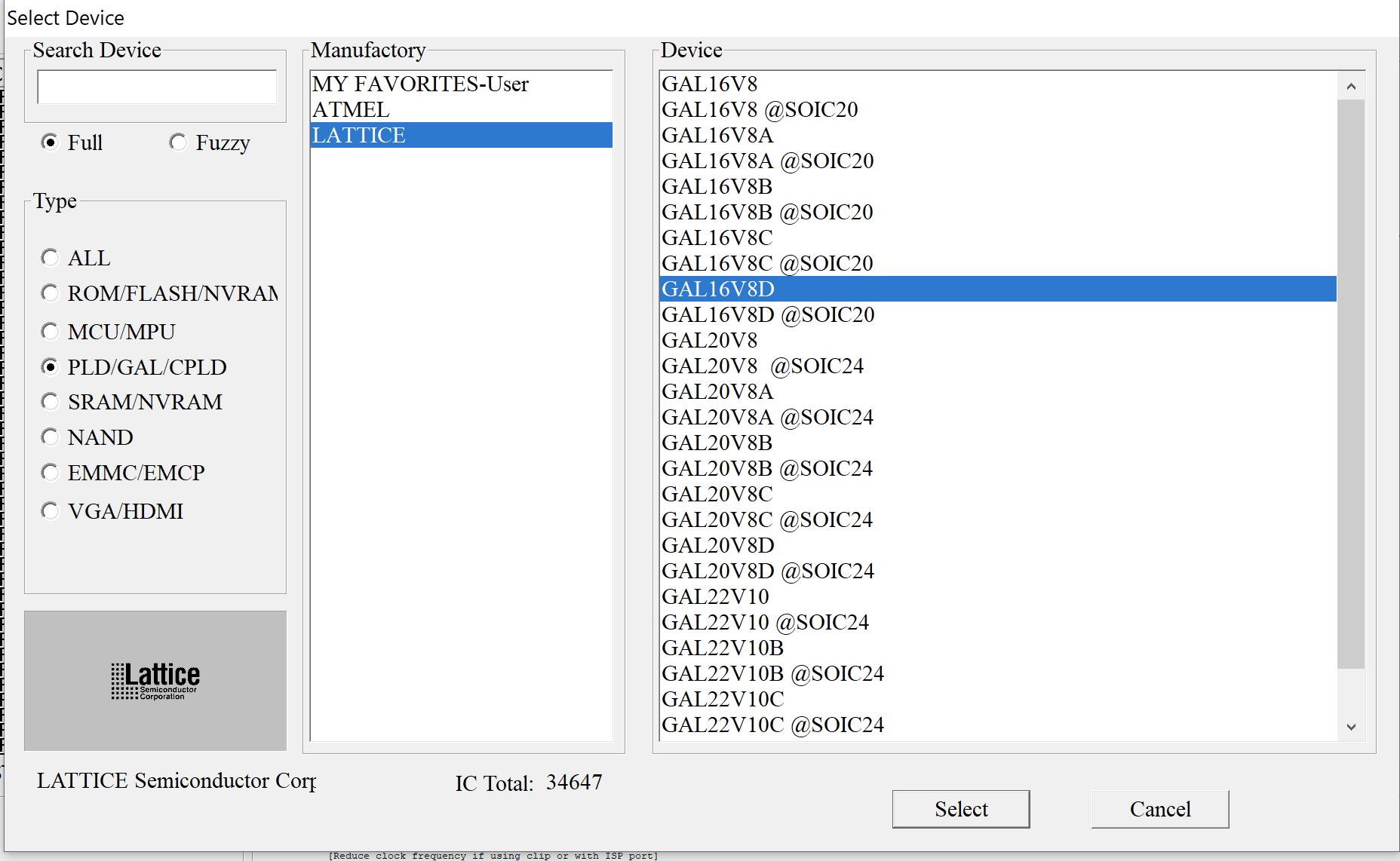

Aperto il programma, premere sul pulsante “Select IC” e selezionare l’integrato da programmare. Nel caso di questo articolo selezioniamo la GAL16V8D.

T48 Programmer Xgpro IC

A questo punto è necessario aprire il JEDEC da programmare sulla GAL. Cliccare su “File->Open File” e selezionare il file JEDEC precedentemente creato. Il file verrà caricato e verrà mostrato nella finestra principale del software.

T48 Programmer Xgpro JEDEC

Per la maggior parte delle configurazione lasciare le “Options” come nell’immagine precedente. Si rimanda alla guida di XGpro per approfondire il significato di ognuna delle voci.

A questo punto non ci rimane che effettuare la programmazione. Cliccare su “Device->Program” ed osservare l’immagine create da XGpro (“Location in Socket”).

T48 Programmer Xgpro Program

Inserire la GAL nel programmatore esattamente come mostra l’immagine e premere su “Program”. Attendere la fine del processo (durata di pochi secondi) con l’indicazione di “Success”.

Se sono state seguite la indicazioni precedenti, ovvero non è stata creata una GAL protetta, è possibile rileggere il contenuto della GAL per verificare se i dati riletti sono uguali al file JEDEC programmato. Per farlo cliccare su “Device->Read” e premere il tasto “Read”. Attendere l’operazione e dopo pochi secondi il binario riletto verrà mostrato nella finestra principale di XGpro dal quale può essere salvato e confrontato con il JEDEC.

Tutte le operazioni sono stata completate e la nostra GAL è pronto ad essere utilizzata. Non ci rimane che toglierla dal programmatore ed inserirla nella scheda elettronica finale per provarla incrociando le dita…ma questa è un’altra storia.

Saluti a tutti e buone ferie!!!

ciao, sto avendo difficoltà nella programmazione di una lattice gal16v8. La lettura e la cancellazione funzionano ma durante la programmazione in fase di verifica ottengo :

PP Version : 12.63 Model : T48

Device : GAL16V8

Pins Detected Passed!

Erase Chip….Timer : 828ms

Programing Fuse Bits completed ….Timer :3375 ms

Verify Error! FUSE bit:0 Buff_val: 1 IC_val: 0

Programming Stopped!

Ho provato sia con la porta usb del pc, sia con un hub alimentato. Hai qualche suggerimento? Grazie

Ciao, la programmazione sembra andare a buon fine ma l’errore è solo sulla successiva verifica. A seconda delle impostazioni di configurazione non è detto che una GAL sia rileggebile in particolar modo se hai impostato di proteggere il codice. E’ proprio perchè le GAL sono non rileggibili che praticamente tutte le GAL non sono facilmente clonabili. Verifica di non aver impostato nessun bit di protezione durante la programmazione.

Saluti